Thursday 4 November, 2021, 11:33 - Amateur Radio, Broadcasting, Licensed, Pirate/Clandestine, Electronics

Posted by Administrator

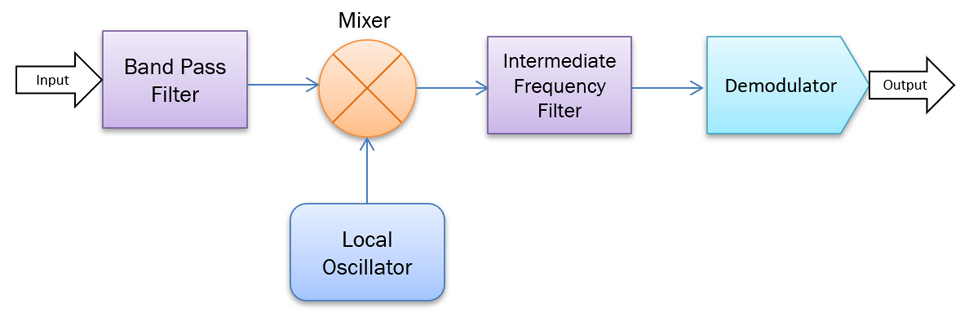

Now that the design of the transmitter has been completed, it's time to turn attention to a receiver. The diagram below shows the blocks which make up a receiver.Posted by Administrator

This works as follows:

- The incoming signal is first sent through a band-pass filter. The job of this filter is to ensure that only signals on the frequency (or frequencies) of interest are sent to the receiver. This makes the job of the receiver more straightforward and, in particular, needs to ensure that signals on the receiver's 'image' frequency (more of which later) are stopped from entering the next stages.

- Jumping to the end of the receiver, a second filter, the intermediate frequency (IF) filter has the job of filtering out any signals on frequencies adjacent to the one that is to be received. This filter has a much narrower frequency response than the band-pass filter at the receiver's input. For a wide-band FM signal, this would typcally have a bandwidth of 250 kHz, whereas the band-pass filter may cover 10 MHz or more.

- The de-modulator has the job of turning the received signal into some form of output. In the case of an FM receiver, this is audio, but this could equally be a digital output if the transmission was in some digital format.

- Sitting between the band-pass filter and the IF filter is a mixer, which is fed both the incoming received signal and some other frequency, usually generated by either a crystal (for a fixed frequency receiver) or by a PLL. This oscillator generating this signal is known as the local oscillator (LO). The mixer operates on the 'heterodyne' principal (invented in 1901 by Reginald Fessenden which is a story worthy of a future post). This mixer is non-linear and as such will 'mush up' the signals and produce all manner of other signals. If the incoming signals are two frequencies f1 and f2, then amongst other things, the mixer will produce 2xf1, 2xf2, f1-f2 (or vice versa), f1+f2 and many other variants. Of most interest to us are f1+f2 and f1-f2. If we take either of these outputs to be the frequency at the centre of the IF filter (usually 10.7 MHz), and f1 is the incoming signal, then if we set f2 at 10.7 MHz above or below the incoming signal frequency, one of the outputs from the mixer will be the IF frequency.

- Assume that the wanted receive frequency is 100 MHz and that the IF frequency is 10.7 MHz, then the LO needs to be at either 89.3 MHz (100-10.7) or 110.7 MHz (100+10.7).

- However, if the LO is at 89.3 MHz, the receiver will perform equally well, not just at 100 MHz but at 10.7 MHz below 89.3, i.e. 78.6 MHz (89.3-10.7). It is the job of the band-pass filter, therefore, to ensure that any signals at 78.6 MHz are rejected and that only the 100 MHz signal passes to the mixer.

- A similar situation occurs if the LO is at 110.7 MHz, as the receiver will then also receive signals at 121.4 MHz (110.7+10.7).

Choosing the correct LO frequency is not trivial and it is important to consider the image frequency. Take a receiver tuned to 71.6 MHz. This would have two possible image frequencies, depending on whether the LO is 10.7 MHz below or above 71.6 MHz. If the LO is below (i.e. 60.9 MHz) then the image frequency would be 50.2 MHz. If the LO is above (i.e. 82.3 MHz) then the image frequency would be 93 MHz. In the first instance the image frequency is right on top of the most active part of the amateur radio 6 metre band, and in the second it is on an FM band frequency. Either of these may lead to interference, and a well designed band-pass filter would be needed to ensure that only the wanted frequency was passed through.

One other important consideration is that receivers are, by their nature, very sensitive devices. Incoming signals as low as 1 microVolt are sufficient to produce an output. This means that very careful attention needs to be paid to the design, to ensure that the minimum of additional noise or unwanted signals are produced. This is especially the case if a PLL is used as the LO. The PLL needs to be clean. As discussed previously, pre-scalers used in PLL's can be very noisy, and care needs to be paid to ensure that none of the output from the pre-scaler is in any way capable of getting into the receiver. In addition, and digital signals (such as the output from the pre-scaler) need to be routed on tracks as short as possible, as, being square waves, they are full of harmonics which could easily fall on a frequency which would interfere with the receiver.

Lots to think about then, and in ensuing installments of this series, the additional building blocks needed for a receiver will be considered.

add comment

( 228 views )

| permalink

|

( 2.7 / 929 )

( 2.7 / 929 )

( 2.7 / 929 )

( 2.7 / 929 )

Monday 25 October, 2021, 19:46 - Amateur Radio, Broadcasting, Licensed, Pirate/Clandestine, Electronics

Posted by Administrator

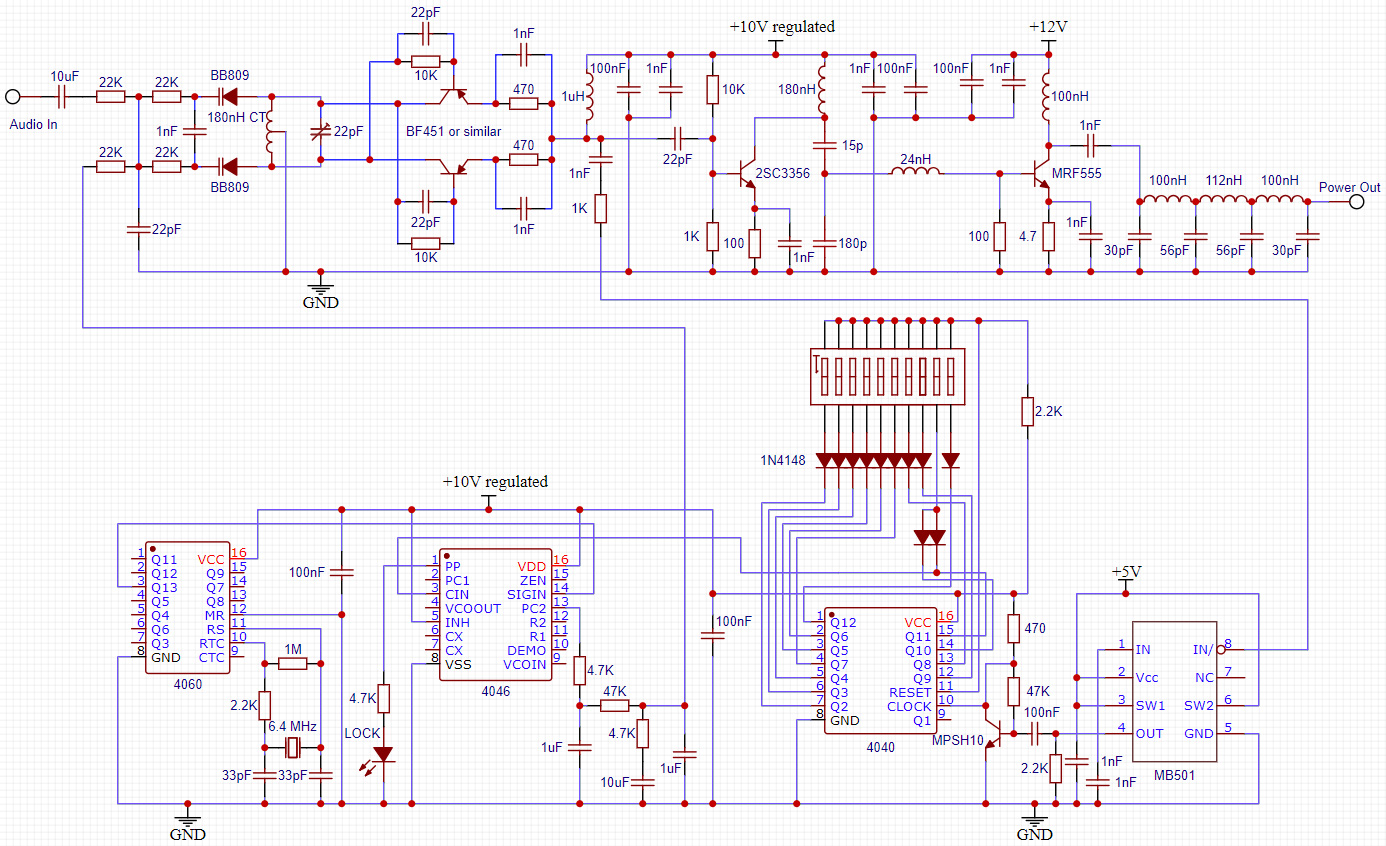

And so here it is, the completed 1 Watt phase locked loop (PLL) FM transmitter. The transmitter part is as exactly as described in part 12, so in this installment of 'How not to design transmitters and receivers' we shall examine the full transmitter including the phase locked loop (PLL). Posted by Administrator

Here's how it works... Some of the signal from the voltage controlled oscillator (VCO) has been tapped off via a 1 K resistor to reduce the amount that is fed to the pre-scaler. The oscillator provides more than sufficient output to feed both the pre-scaler and the transmitter, so there is no need in this case for any additional buffer between the VCO and the pre-scaler. The pre-scaler (the MB501L) is set to divide by 64 meaning, for example, that with the VCO operating at 100 MHz, the output will be at 1.5625 MHz. A single transistor NPN level buffer has been used between the pre-scalar and the 'divide by N' chip to increase the voltage from the approximately 1.5V peak-to-peak signal at the output of the MB501L to the full supply range needed for the CMOS chip.

Next the reference oscillator. A 4060 IC has been used, with a 6.4 MHz crystal. The division ratio of the 4060 that has been selected is 214 (oddly labelled Q13 in the schematic), or 16384, yielding an output from this chip at 390.625 Hz.

In order for the loop to lock, it is therefore necessary to divide the 1.5625 MHz coming from the pre-scaler down to 390.625 Hz. At an operating frequency of 100 MHz, this requires a division ratio of exactly 4000. If we wish the transmitter to operate over the whole of the FM band, for example, then we will require division ratios ranging from 3500 (for 87.5 MHz) to 4320 (for 108 MHz). The binary values for these ratios are shown in the table below.

| Digits | 212 | 211 | 210 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 4096 | 2048 | 1024 | 512 | 256 | 128 | 64 | 32 | 16 | 8 | 4 | 2 | 1 | |

| 3500 (87.5) | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 |

| 4000 (100.0) | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 4320 (108.0) | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

A couple of things have been highlighted:

- Bits 10 and 11 (1024 and 2048) are either both '1' or both '0'. This holds true across the whole of the frequency range from 87.5 to 108.0 (indeed it holds true from binary 3072 [76.8] MHz to 5119 [127.975 MHz]). These two bits (coloured orange) can therefore be linked together.

- Bits 0 and 1 (1 and 2) are both '0' in both cases. This holds true for any frequency which is a mulitple of 100 kHz. These two bits can therefore be ignored.

A feed from Q11 has been taken from the chip to feed into the phase comparator. The phase comparator used is the good old (literally) 4046. This has two outputs of interest:

- The 'Pulse Phases' (PP) output (pin 1) goes low every time the phase comparator outputs an error voltage, meaning that if the loop is in lock, this pin sits at a positive voltage. Connecting an LED from this pin to ground (through a suitable current limiting resistor) thus acts as a lock detector, the LED growing increasingly bright as the PLL is locked. It can be informative to connect a headphone to this pin (via, say, a 4.7K resistor) as you will get an auditory indication of the two input frequencies and how far apart they are.

- The 'Phase Comparator 2' (PC2) output (pin 13) is used as the output of the phase detector itself. This pin will output a logic 'high' pulse if the divided down phase/frequency of the loop is lower than the reference frequency and a logic 'low' if the phase/frequency is too high. Suitably filtered, this output can be fed to the varicap diodes in the loop to correct the loop frequency.

No circuit for producing the necessary regulated 10 Volt (or 5 Volt) supply has been shown: If you can't work out how to produce such a voltage, there's little chance of you being able to build the transmitter correctly.

You have probably noted that this series is entitled 'How not to design transmitters and receivers', and so far all that has been covered are transmitters. So, in ensuing instalments, the building blocks required to build a receiver together with the many pitfalls which can trap you when doing this will be discussed.

Monday 4 October, 2021, 23:25 - Amateur Radio, Broadcasting, Licensed, Pirate/Clandestine, Electronics

Posted by Administrator

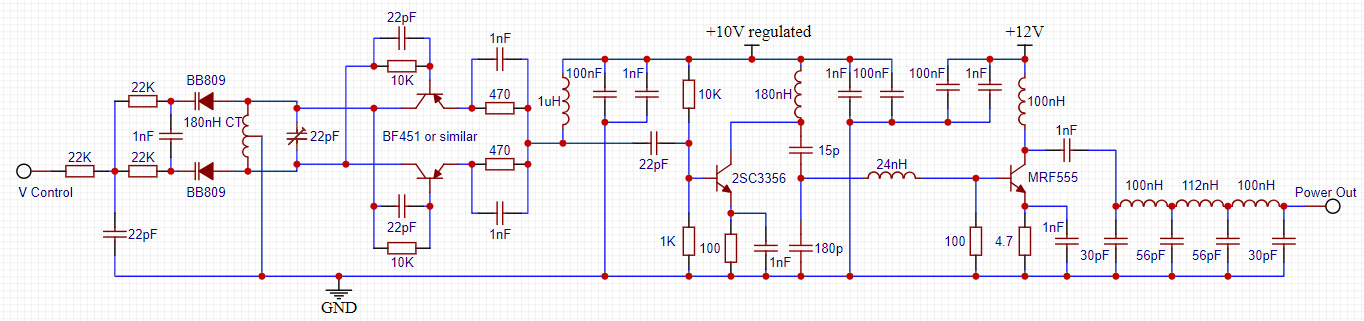

The previous parts of the "How not to design transmitters and receivers" series have described all the design decisions and blocks which need to go together to produce a 1 Watt wideband FM transmitter. It is now time to start putting those blocks together into a full-blown design. Posted by Administrator

First up is the 1 Watt transmitter chain itself, composed of:

- a voltage controlled oscillator (VCO) as described in part 1

- a buffer amplifier which is not totally dissimilar to those described in part 6,

- a matching circuit between the buffer and the power amplifier, as described in part 3,

- a 1 Watt power amplifier, based on a device identified in part 2, and

- a low-pass filter, as described in part 9.

The VCO should be set to oscillate at half the wanted output frequency. The '2f' component of this is then passed to the buffer which is formed of the 2SC3356. The 22pF capacitor between them is not critical. Other transistors which can produce around 100mW of power would be equally suitable in the buffering role, such as the MPSH10. The output of the buffer is fed into the power amplifier and then through a low pass filter. The output transistor (the MRF555) can also be replaced by different devices, however the matching network between the buffer and the output stage may require alteration.

No phase locked loop (PLL) circuitry is yet shown, this will follow in an ensuing post. As illustrated, the design is called a 'free running' oscillator meaning that its output frequency is set only by the control voltage applied to its input, the value of the centre-tapped inductor in the circuit, and the variable capacitor which sits across it. This design is relatively stable and after settling down has an accuracy of better than a few kHz at an output frequency of 100 MHz, as long as the control voltage remains constant and the temperature isn't allowed to drift too much.

In operation, the BF451's should draw around 10 mA each, the 2SC3356 (or equivalent) should draw around 15 mA and the output device in the region of 150mA. If constructing a prototype based on this schematic, ensure that good radio frequency (RF) construction principles are adhered to, in particular:

- The leads of all components should be kept as short as possible, and certainly not be allowed to exceed 1 cm in length. This is because a simple piece of wire will act as an inductor at RF and introduce unwanted reactance to the circuit.

- Ideally, the circuit should be built over a solid ground-plane which acts as the ground connection. A piece of un-etched copper-clad printed circuit board (PCB) material will do the job handsomely.

Thursday 16 September, 2021, 16:18 - Amateur Radio, Broadcasting, Licensed, Pirate/Clandestine, Electronics

Posted by Administrator

In an earlier 'How not to design transmitters and receivers' it was blithely stated that the reference oscillator part of a phase locked loop (PLL) was a relatively trivial undertaking. And... it is. All that needs to be decided is what the reference frequency is going to be.Posted by Administrator

Throughout these series of articles, a reference frequency of 100 kHz has been used in order to illustrate how a variable frequency PLL operates. However, this would require that the output frequency is fed directly into the 'divide by N' block, and as has also been discussed, these devices do not usually operate at frequencies as high as 100 MHz, indeed many of the purpose-designed divide by N chips (such as the TC9122P) will only cope with input frequencies as high as 10 to 15 MHz. In addition, as was discussed in part 5, the lower the reference frequency, the less the PLL will see modulation as a frequency error and try and correct it. A reference frequency of 100 kHz is therefore both difficult to work with (due to the divide by N frequency limitations) and too high (due to the PLL trying to correct modulation).

How high should the reference frequency be then? In many PLL designs for FM transmitters, this is often set to be in the order of 10 kHz, though some designs are nearer 1 kHz. For the Wireless Waffle lockdown project, it was decided to use an even lower frequency, so that the low frequency audio response of the PLL could be as flat as possible.

To define the exact frequency, the amount by which the prescaler initially divides down the output frequency must be factored in. The previously discussed MB501L can be set to divide by 64 or 128. If either of these were immediately followed by a divide by N, which could count in steps of 1 and with each step being 100 kHz, then the maximum reference frequency would be either 1.5625 kHz (100 kHz / 64) or 781.25 Hz (100 kHz / 128). The reference frequency could be lower than this if, for example, the divide by N used a higher division ratio (for example, counting in steps of 2). To allow for 25 kHz steps, which are used in some other audio applications such as studio-to-transmitter links, a reference frequency of 390.625 Hz was chosen (i.e. 25 kHz / 64). Note that this means that for each 100 kHz step, the divide by N counter has to be incremented by 4, not 1.

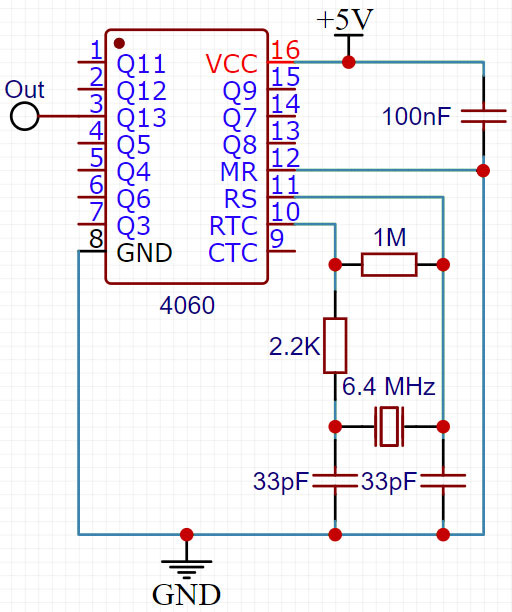

The simplest way of generating a reference frequency is to use the tried and tested 4060 IC as shown in the circuit on the right. The 4060 has a built in oscillator (which can be used with quartz crystals such as in this application, or as just with resistors and capacitors) as well as having a binary counter that can easily produce outputs divided by multiples of 2. Even the standard CMOS version of this chip will oscillate at frequencies up to around 8 MHz with a 5 Volt power supply and higher still if the supply voltage is increased.

The simplest way of generating a reference frequency is to use the tried and tested 4060 IC as shown in the circuit on the right. The 4060 has a built in oscillator (which can be used with quartz crystals such as in this application, or as just with resistors and capacitors) as well as having a binary counter that can easily produce outputs divided by multiples of 2. Even the standard CMOS version of this chip will oscillate at frequencies up to around 8 MHz with a 5 Volt power supply and higher still if the supply voltage is increased.A crystal with a frequency of 6.4 MHz is easy to source (being a not-uncommon clock frequency) and needs to be divided by 16384 (or 214) to produce an output at the required reference at 390.625 Hz. The 4060 has an output which divides by 214 on pin 3 so a simple crystal oscillator and divider circuit can be made from this chip alone.

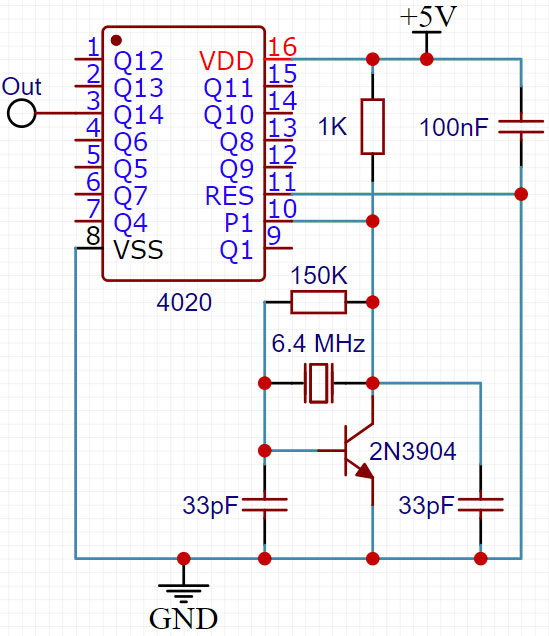

Other CMOS divider chips (such as the 4020, 4024 or 4040) can also be used for dividing down a fixed frequency oscillator but need a stand-alone crystal oscillator to drive them. An example of this arrangement is shown on the left.

Other CMOS divider chips (such as the 4020, 4024 or 4040) can also be used for dividing down a fixed frequency oscillator but need a stand-alone crystal oscillator to drive them. An example of this arrangement is shown on the left.Note that the value of resistors around the transistor used as the oscillator are somewhat critical. The exact current flowing through the transistor is not that critical (anywhere in the region of 2 to 5 milliAmps should be OK) however the transistor needs to be biassed such that when it is not oscillating, the collector voltage is close to half the supply voltage. This will mean that when oscillating the output swings equally above and below half the supply voltage, which the CMOS counter, whose input thresholds are similarly symmetrical, will count properly. In the case of the transistor being biassed such that the output when not oscillating sits at say, 3/4 of the supply voltage, it is possible that the peak-to-peak output swing may be reduced and may not be sufficient to drive the CMOS chip. These resistor values will be different depending on the exact transistor used (actually the specific DC current gain, β, or hFE of the transistor). As with many electronic design problems these days, there's an online tool to help calculate the necessary resistor values..

And so, the end is near, and that final curtain is nearly ready to be opened to a blaze of audience applause. In the next article in this series, everything learnt so far will be soldered together into a single circuit diagram (or schematic, whichever is your preference). And then it will be time to start to think about receivers, and their associated building blocks. Some say that radio frequency (RF) design is a bit of a black art, insofar as there are so many hurdles which can trip you up along the way (if that isn't a badly mixed metaphor). For transmitters, the biggest problems come from unwanted harmonics and crazy spurious oscillations. In receivers there are these things to deal with, but also the need to have a nice clean and distortion path from the input to the output so that the wanted signal can be received, and any unwanted signals can be rejected. Nobody said it was easy.

And so, the end is near, and that final curtain is nearly ready to be opened to a blaze of audience applause. In the next article in this series, everything learnt so far will be soldered together into a single circuit diagram (or schematic, whichever is your preference). And then it will be time to start to think about receivers, and their associated building blocks. Some say that radio frequency (RF) design is a bit of a black art, insofar as there are so many hurdles which can trip you up along the way (if that isn't a badly mixed metaphor). For transmitters, the biggest problems come from unwanted harmonics and crazy spurious oscillations. In receivers there are these things to deal with, but also the need to have a nice clean and distortion path from the input to the output so that the wanted signal can be received, and any unwanted signals can be rejected. Nobody said it was easy.